성과

2025 IEEE IEDM 학회 참가보고서/포항공과대학교/정성수/20251206~202510

전시회명 | IEEE IEDM 2025 | |||||

전시장소 | 미국 (샌프란시스코) | 부스 No. | 해당 시 | |||

참가일자 | 2025. 12. 06. ~ 2025. 12. 10. | |||||

참가자 | 소속대학 | POSTECH | 학위과정 | 석사과정 | 학기 | 2 |

소속학과 | 전자전기공학과 | 이름 | 정성수 | 지도교수 | 백록현 | |

전시품명 | Machine Learning Oriented Compact Model Platform for Technology Development and Circuit Design | |||||

참관내용 | TSMC에서 제안한 머신러닝(ML) 기반의 Compact Model Platform에 대한 연구 결과이다. 기존의 물리 기반 수식 모델(Physics-based equation)이 갖는 미세 공정에서의 정확도 한계를 극복하기 위해, 물리 수식에 신경망(Neural Network)을 결합한 CPNN (Compensation Neural Network) 구조를 도입하여 트랜지스터의 전기적 특성 예측 정확도를 대폭 향상시켰다

특히 BEOL 공정에서 복잡한 레이아웃 패턴에 따른 기생 성분(Parasitic R/C)을 추출하기 위해 CNN 기반 모델링을 적용한 점이 인상적이었다. 이는 상용 3D Field Solver 수준의 정확도(C_3D, R_3D와 일치)를 확보하면서도 연산 속도를 획기적으로 개선하여, 공정 Variability를 고려한 통계적 분석의 효율성을 입증하였다. 또한, 시뮬레이션 비용을 줄이기 위해 도메인 지식을 활용한 Active Learning 기법을 도입하여 High-Sigma 코너를 효율적으로 예측하는 방법론을 제시하였다.

본 연구는 TSMC Model Interface 표준을 통해 시뮬레이터와 ML 모델을 연동하고, Agentic LLM을 활용하여 모델링 워크플로우를 자동화하려는 시도를 포함하고 있다. 이는 시스템 반도체 설계 시 발생하는 Design-Technology Co-Optimization (DTCO) 난제를 해결할 실질적 솔루션의 가능성을 제시하였다.

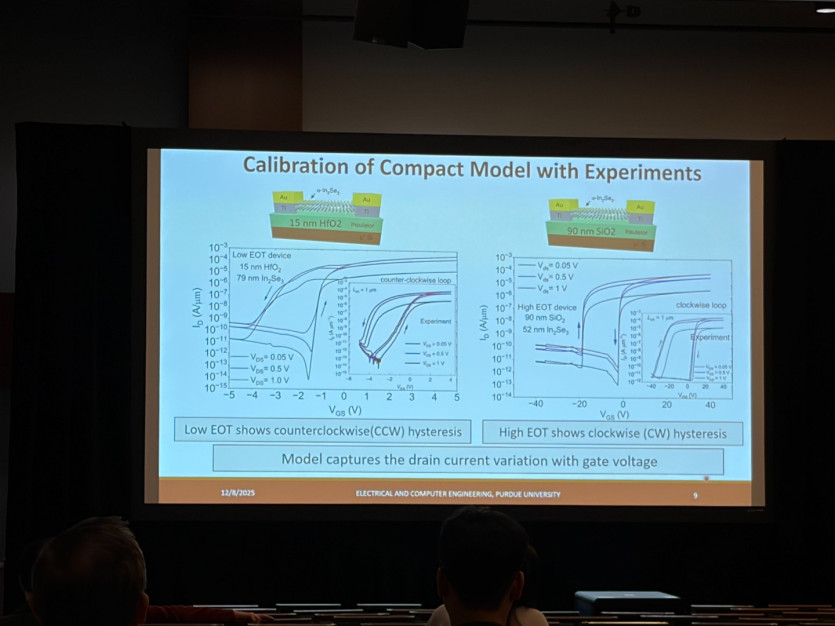

이 밖에도 IEDM 2025 학회에 참석하여 Compact Model, 3D NAND, Logic Technology 세션을 집중적으로 청취하며 최신 기술 동향을 파악하였다. 시스템 반도체의 고성능화와 3차원 이종 집적 추세에 따라, 공정과 설계를 잇는 정밀 모델링 기술이 필수적임을 재확인했다. 특히 이번 참관을 통해 단순한 소자 특성 개선을 넘어, ML 기술을 접목한 PPA(Power, Performance, Area) 최적화 방법론에 대한 통찰을 얻었으며, 이를 바탕으로 향후 연구 과제의 방향성을 구체화하는 성과를 거두었다. | |||||