성과

2025 IEDM 학회 참가보고서/포항공과대학교/홍기륜/20251206-20251210

전시회명 : 2025 IEDM (International Electron Devices Meeting)

전시장소 : San Francisco, CA

참가일자 : 2025/12/07

참가자 : 포항공과대학교 전자전기공학과 박사과정 홍기륜 (지도교수 백록현)

전시품명: (SC1-1) Device Technologies for GAA Scaling and Emerging Alternatives

참관내용: 스마트폰, 웨어러블 기기, HPC 서버와 같은 모바일 및 고성능 컴퓨팅 기기에서 전력 효율, 성능 및 면적 최적화에 대한 수요가 증가함에 따라 논리 기술의 지속적인 발전이 이루어졌습니다. 기존의 평면형 Si-MOSFET는 스트레스 엔지니어링 및 고유전율 금속 게이트와 같은 주요 혁신을 통해 무어의 법칙을 성공적으로 따랐으며, 결국 FinFET 및 GAA(Gate-All-Around) 나노시트 FET와 같은 3D 구조로 발전했습니다. 특히, GAA 나노시트 소자 기술로의 전환은 3nm 및 2nm 노드에서 거의 완료되었으며, 고성능 컴퓨팅 애플리케이션을 위한 플랫폼 기술을 향상시키는 BSPDN(Back Side Power Delivery Network)의 도입과 함께 진행되고 있습니다. FinFET 세대와 마찬가지로 GAA 소자는 향후 10년 이상 주류 기술로 유지될 것으로 예상됩니다. 그러나 셀 높이의 지속적인 축소는 포크시트 및 3D 적층 FET 아키텍처로의 전환을 필요로 할 것입니다. 본 short course에서는 GAA 나노시트 소자 기술의 개발, 진화, 그리고 현재의 구조적 한계를 극복하고자 하는 잠재적인 후속 기술에 대해 살펴봅니다.

전시회명 : 2025 IEDM (International Electron Devices Meeting)

전시장소 : San Francisco, CA

참가일자 : 2025/12/08

참가자 : 포항공과대학교 전자전기공학과 박사과정 홍기륜 (지도교수 백록현)

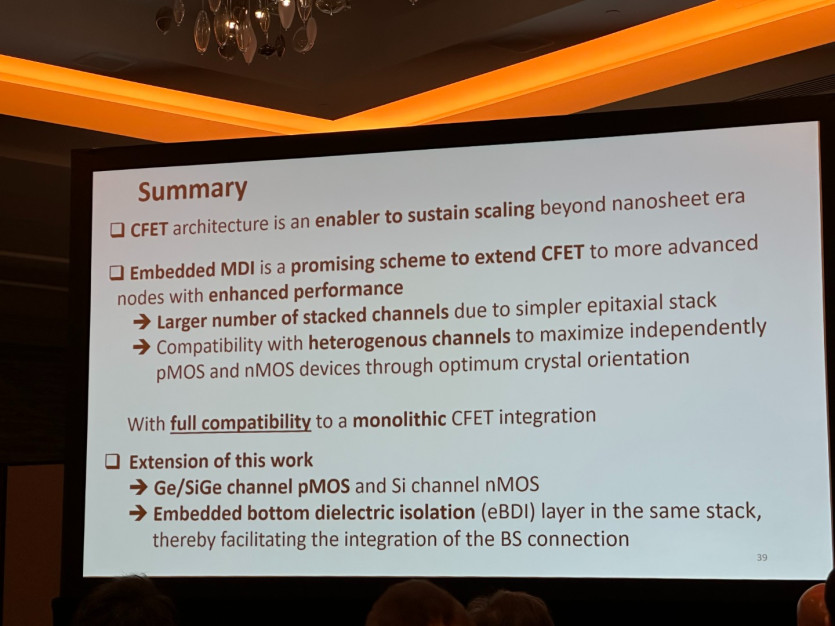

전시품명: (Session 2) Gate-All-Around Technology, CFET and DTCO

참관내용: 본 세션에서는 반도체 산업이 3nm 노드에서 FinFET 스케일링 한계를 넘어 전환함에 따라 게이트 올 어라운드(GAA) 및 3D 적층 트랜지스터 기술의 중요한 발전을 소개합니다. 이 세션에서는 단기적인 GAA 구현과 미래의 CFET 아키텍처를 다루는 8편의 논문을 발표합니다. 삼성은 GAA 기술이 지속 가능한 AI 애플리케이션에 적합함을 입증하고, 포크시트 및 3D 적층 FET를 포함한 미래 로직 아키텍처의 기반으로서의 역할을 강조합니다. IMEC는 n/p형 최적화를 위한 서로 다른 결정 방향을 갖는 하이브리드 채널 모놀리식 CFET, A7에서 A3 노드로의 오메가 게이트 포크시트 구조를 통한 공격적인 셀 높이 스케일링, 동일 성능에서 46% 면적 감소를 달성하는 포괄적인 DTCO, 그리고 향상된 도핑 활성화를 통해 100% 성능 향상을 달성하는 초저온(<350°C) SiGe:B 에피택시 등 다양한 연구 결과를 발표합니다. TSMC는 최초의 기능성 링 발진기와 48nm 미만 피치의 가장 작은 SRAM 비트 셀을 통해 회로 수준의 CFET 기술 성숙도를 선보였습니다. IBM은 핵심 스케일링 기술에 대한 두 편의 논문을 발표했습니다. 첫 번째는 후면 전력 공급을 통한 100nm 미만 셀 높이 라이브러리 최적화로, 매우 작은 크기에서도 실현 가능한 성능을 입증했습니다. 두 번째는 SiGe 채널 구현을 통해 채널 저항을 34% 감소시켜 전류를 17% 향상시킨 것입니다. 이 논문들은 GAA(Global Area Assessment)가 기존 공정과의 호환성을 유지하면서 실용적인 단기 솔루션 역할을 하는 반면, 후면 전력 공급 및 이종 통합 기능을 갖춘 CFET 기술은 면적 효율성 향상과 성능 개선을 통해 무어의 법칙에 따른 지속적인 스케일링을 가능하게 하는 길을 제시한다는 것을 보여줍니다.

전시회명 : 2025 IEDM (International Electron Devices Meeting)

전시장소 : San Francisco, CA

참가일자 : 2025/12/09

참가자 : 포항공과대학교 전자전기공학과 박사과정 홍기륜 (지도교수 백록현)

전시품명: (Session 18) NAND Technology

참관내용: NAND 기술 세션에서는 3D NAND, FeNAND, 그리고 공정 및 구조 설계 혁신 분야의 최신 산업 발전을 조명하는 8편의 논문이 발표됩니다. 세션은 SK하이닉스의 최첨단 기술인 321층 3D NAND의 통합 및 특성 분석에 대한 발표로 시작됩니다. 이어서 삼성은 9세대 VNAND에 적용된 Mo 기반 워드라인 금속 통합 기술을 발표합니다. SK하이닉스는 지속적인 스케일링을 지원하는 176층 3D NAND에 절연 전하 트랩층을 통합하는 연구 진행 상황을 공유합니다. KAIST는 메모리 윈도우 향상을 목표로 하는 BON 터널링층에 대한 연구를 발표합니다. SK하이닉스는 또한 PLC(수동 논리 셀) 기능을 구현하기 위한 새로운 분할 셀 통합 방식을 소개합니다. 세션 후반부에는 FeNAND에 대한 내용이 집중적으로 다뤄집니다. 마이크론은 넓은 메모리 윈도우와 뛰어난 데이터 유지력을 특징으로 하는 저전압 수직형 FeNAND를 선보일 예정이며, 게이트 스택 최적화를 통해 읽기 방해 및 간섭 문제를 해결할 것입니다. KAIST는 2nm IGZO 트랩층을 적용한 FeNAND 셀을 소개하고, 트랩 프로파일 엔지니어링을 통해 높은 내구성과 데이터 유지력을 달성할 것입니다. 마지막으로, KAIST는 초박형 Mo와 3.5nm 이하 HZO를 사용하여 넓은 메모리 윈도우와 효율적인 트리플 레벨 셀(TLC) 동작을 구현하는 확장 가능한 NC-NAND 설계를 선보일 예정입니다.

전시회명 : 2025 IEDM (International Electron Devices Meeting)

전시장소 : San Francisco, CA

참가일자 : 2025/12/10

참가자 : 포항공과대학교 전자전기공학과 박사과정 홍기륜 (지도교수 백록현)

전시품명: (Session 33) BEOL-Compatible Devices and Interconnect Technology

참관내용: BEOL 호환 소자, 인터커넥트 및 전력 공급 시스템 분야의 주요 발전을 조명하는 8편의 논문 세션입니다. 스위치드 커패시터, MIM 및 트랜지스터와 같은 BEOL 호환 소자를 소개합니다. 구리를 대체할 루테늄 인터커넥트를 구현하기 위한 결정 구조 및 통합 기술의 발전 또한 소개됩니다. 3D SoC용 칩 간 인터커넥트 기술 및 열 관리를 위한 CNT TSV 활용을 집중적으로 다루기도 합니다.